到51单片机的时钟首先想到51时怎么工作的呢?微型控制器要想工作必须要有一个“动力”,对于51单片机来说,这个“动力”就是时钟源。一般应用上会外接一个12MHz的晶振作为时钟源。

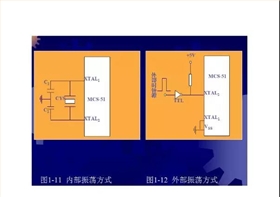

一般第一种接法用的比较多。选择内部震荡方式时晶振旁边有两个小电容。这两个电容叫晶振的负载电容,分别接在晶振的两个脚上和对地的电容,一般在几十皮发。它会影响到晶振的谐振频率和输出幅度。晶振的负载电容=[(Cd*Cg)/(Cd+Cg)]+Cic+△C式中Cd,Cg为分别接在晶振的两个脚上和对地的电容,Cic(集成电路内部电容)+△C(PCB上电容)经验值为3至5pf。

各种逻辑芯片的晶振引脚可以等效为电容三点式振荡器。晶振引脚的内部通常是一个反相器, 或者是奇数个反相器串联。在晶振输出引脚 XO 和晶振输入引脚 XI 之间用一个电阻连接, 对于 CMOS 芯片通常是数 M 到数十M 欧之间。 很多芯片的引脚内部已经包含了这个电阻, 引脚外部就不用接了。这个电阻是为了使反相器在振荡初始时处与线性状态, 反相器就如同一个有很大增益的放大器, 以便于起振。

为什么要选择12MHz的晶振作为时钟源呢?

这就要说51单片机内部的几个周期了:指令周期、机器周期、时钟周期、振荡周期。振荡周期是指为单片机提供定时信号的振荡源的周期或外部输入时钟的周期。

时钟周期又称作状态周期或状态时间S,它是振荡周期的两倍,分为P1节拍和P2节拍,通常在P1节拍完成算术逻辑操作,在P2节拍完成内部寄存器之间的数据传送操作。(注意P1 和P2的相位关系 )

一个机器周期由6个状态组成,如果把一条指令的执行过程分作几个基本操作,则将完成一个基本操作所需的时间称作机器周期。单片机的单周期指令执行时间就为一个机器周期。

指令周期是执行一条指令所需的全部时间。MCS-51单片机的指令周期通常由1、2、4个机器周期组成。

对于12MHz的晶振,提供了12M的振荡周期,6M的时钟周期,1M的机器周期。所以此时51单片机的单指令周期为(1/1M)s=1us.这个1us有什么好处呢?后面大家会知道单片机应用中会有各种各样的时序,很多时候需要用一小段程序延时来达到时序要求,而1us的单指令周期比较方便计算延时时间以及确定每条语句的执行时间。应该明确的是单片机执行每条语句用的时间是非常确定的,是1us就是1us不会多一点也不会少一点。

下面说说51单片机的总线扩展:

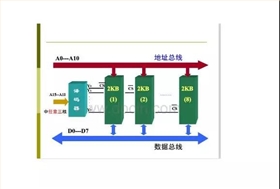

这种结构就是上一篇说到的三总线结构,如图所示

1、数据总线

51 单片机的数据总线为P0 口,CPU 从P0 口送出和读回数据。

2、地址总线

51 系列单片机的地址总线为16 位。

为了节约芯片引脚,采用P0 口复用方式,除了作为数据总线外,在ALE 信号时序匹配下,通过外置的数据锁存器,在总线访问前半周期从P0口送出低8位地址,后半周期从P0 口送出8 位数据。

高8位地址则通过P2 口送出。

3、控制总线

51 系列单片机的控制总线包括(RD)读控制信号P3.7 和(WR)写控制信号P3.6 等,二者分别作为总线模式下数据读和数据写的使能信号。

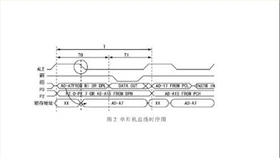

51 单片机总线时序如图 所示。

从图2 中可以看出,完成一次总线( 读写) 操作周期为T,P0 口分时复用,在T0 期间,P0 口送出低8 位地址,在ALE 的下降沿完成数据锁存,送出低8位地址信号。在T1 期间,P0 口作为数据总线使用,送出或读入数据,数据的读写操作在读、写控制信号的低电平期间完成。

需要注意的是,在控制信号( 读、写信号) 有效期间,P2 口送出高8位地址,配合数据锁存器输出的低8 位地址,实现16 位地址总线,即64kB 范围的内的寻址。

由于CPU不可能同时执行读和写操作,所以读、写信号不可能同时有效。

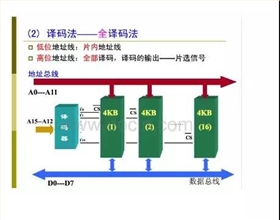

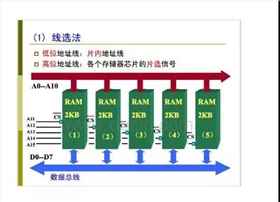

采用这种总线结构按照规定的时序能够最大程度的利用单片机的全部地址线。这就是单片机的编址。编址分为线选法和译码法,译码法分为全译码、部分译码。线选法的优点是简单但是非常浪费地址线;全译码法能够最大程度的利用全部地址线,但是电路很复杂需要一些与非门的配合才行。一般用部分译码法性价比最高,尤其是在外接了存储芯片时部分译码法很方便。

电位器调光板,旋钮调光控制板

电位器调光板,旋钮调光控制板 双色温台灯线路板

双色温台灯线路板 循环定时蜡烛芯片,8小时开16小时关

循环定时蜡烛芯片,8小时开16小时关 电话咨询

电话咨询 产品中心

产品中心 联系丽晶微

联系丽晶微 网站地图

网站地图